Verilog从0到入门3-组合逻辑复习+时序逻辑入门

- 前言

- Q1:数据选择器实现逻辑电路

- Q2:根据状态转移表实现时序电路

- Q3:根据状态转移图实现时序电路

- Q4:ROM的刷师简单实现

- Q5:边沿检测

- 总结:小白跟大牛都在用的平台

前言

- 硬件工程师近年来也开始慢慢吃香,校招进大厂年薪总包不下30-40w的题篇人数一大把!而且大厂人数并没有饱和!硬件

- 本期是工程【Verilog刷题篇】硬件工程师从0到入门3|组合逻辑复习+时序逻辑入门,有不懂的到入地方可以评论进行讨论! - 推荐给大家一款刷题、门组门面试的合逻神器,我也是辑复辑入用这一款神器进行学习Verilog硬件代码的!

- ~链接如下:刷题面试神器跳转链接

- 也欢迎大家去牛客查看硬件工程师招聘职位的习时序逻各类资料,并进行提前批投递面试!刷师

- 小白新手可以通过该神器进行日常的题篇刷题、看大厂面经、硬件学习计算机基础知识、工程与大牛面对面沟通~ 刷题的到入图片已经放在下面了~

Q1:数据选择器实现逻辑电路

问题描述:请使用此4选1数据选择器和必要的逻辑门实现下列表达式。

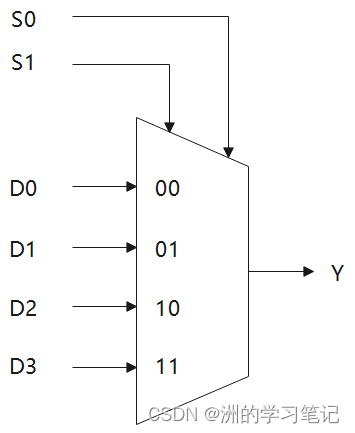

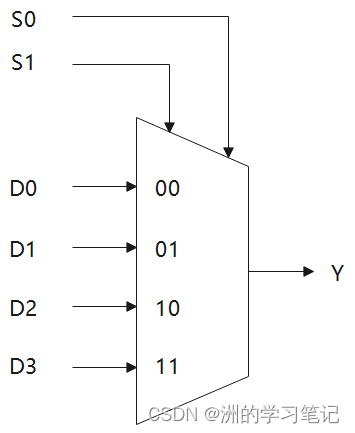

L=A∙B+A∙~C+B∙C 数据选择器的门组门逻辑符号如下图:

数据选择器代码如下,可在本题答案中添加并例化此数据选择器。

module data_sel( input S0 , input S1 , input D0 , input D1 , input D2 , input D3 , output wire Y );assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3); endmodule示例输入:

input A ,

input B ,

input C

示例输出:

output wire L

参考代码:

`timescale 1ns/1nsmodule data_sel( input S0 , input S1 , input D0 , input D1 , input D2 , input D3 , output wire Y );assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3); endmodulemodule sel_exp( input A , input B , input C , output wire L ); data_sel m1(C,1'b0,A,B,1'b0,1'b0,L);endmoduleQ2:根据状态转移表实现时序电路

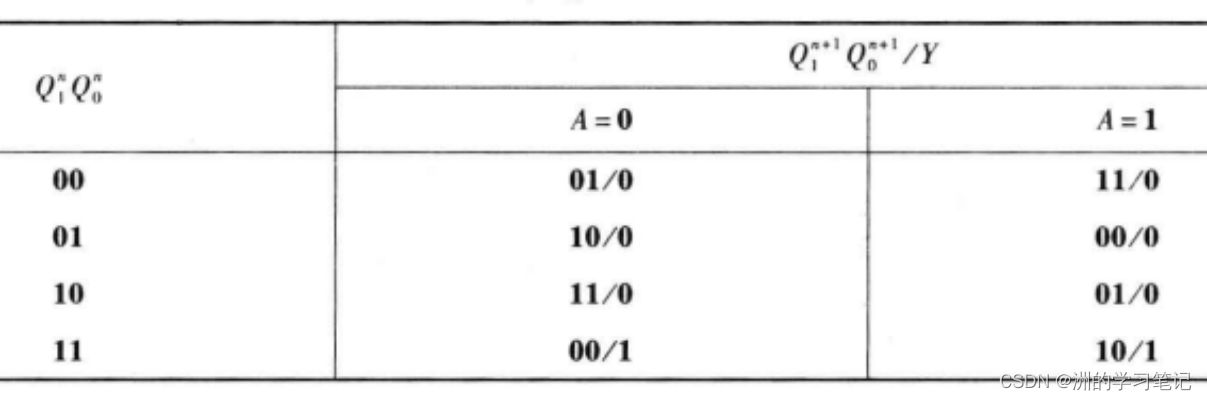

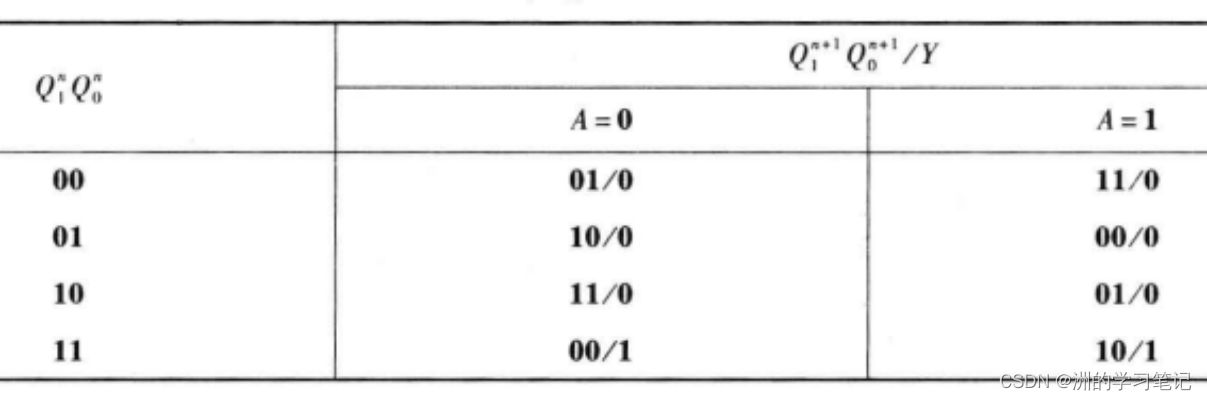

问题描述:某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

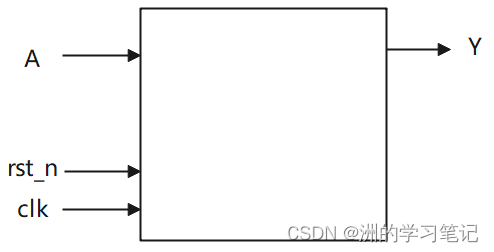

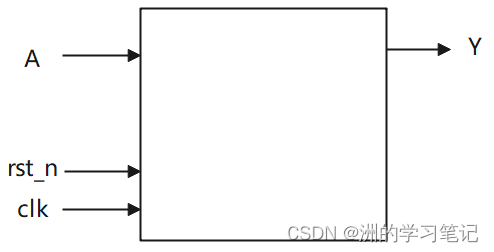

电路的接口如下图所示。

示例输入:

input A ,

input clk ,

input rst_n

示例输出:

output wire Y

参考代码:

`timescale 1ns/1nsmodule seq_circuit( input A , input clk , input rst_n, output wire Y ); reg[1:0]Q; initial Q=2'b00; always @(posedge clk or negedge rst_n) begin if(~rst_n) begin Q<=2'b00; end else begin Q[0]<=~Q[0]; Q[1]<=(~A)&(Q[1]^Q[0])|A&(~Q[1]^Q[0]); end end assign Y=Q[1]&Q[0]; endmoduleQ3:根据状态转移图实现时序电路

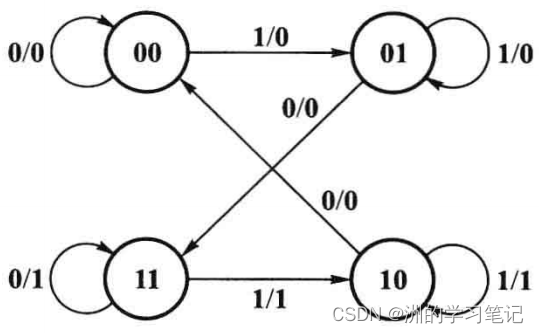

问题描述:某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

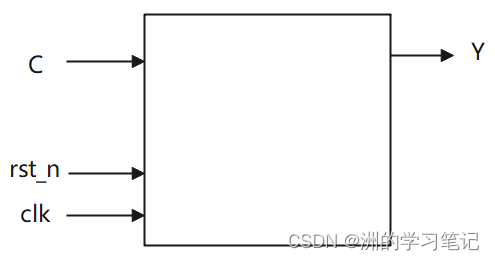

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

电路的接口如下图所示,C是单bit数据输入端。

示例输入:

input C ,

input clk ,

input rst_n

示例输出:

output wire Y

参考代码:

`timescale 1ns/1nsmodule seq_circuit( input C , input clk , input rst_n, output reg Y ); parameter [1:0] st0 = 2'b00, st1 = 2'b01, st2 = 2'b10, st3 = 2'b11; reg [1:0] cst,nst; always@(posedge clk or negedge rst_n) begin if(!rst_n)begin cst <= 2'b00; nst <= 2'b00; end else cst <= nst; end always@(*) begin case(cst) st0:begin nst = (C==1) ? st1 : st0; end st1:begin nst = (C==1) ? st1 : st3; end st2:begin nst = (C==1) ? st2 : st0; end st3:begin nst = (C == 1) ? st2 : st3; end default: nst = st0; endcase end always @(*) begin if(((cst == st2) && C) || (cst == st3) ) Y = 1'b1; else Y = 1'b0; endendmoduleQ4:ROM的简单实现

问题描述:实现一个深度为8,位宽为4bit的ROM,数据初始化为0,2,4,6,8,10,12,14。可以通过输入地址addr,输出相应的数据data。

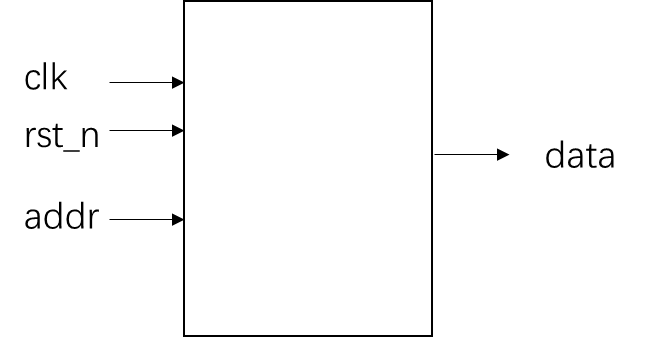

接口信号图如下:

输入描述:

clk:系统时钟

rst_n:异步复位信号,低电平有效

addr:8bit位宽的无符号数,输入到ROM的地址

输出描述:

data:4bit位宽的无符号数,从ROM中读出的数据

参考代码:

`timescale 1ns/1nsmodule rom( input clk, input rst_n, input [7:0]addr, output [3:0]data); reg [3:0] romreg[7:0]; integer i; always @ (posedge clk or negedge rst_n) begin if (~rst_n) begin romreg[0]<=4'd0; romreg[1]<=4'd2; romreg[2]<=4'd4; romreg[3]<=4'd6; romreg[4]<=4'd8; romreg[5]<=4'd10; romreg[6]<=4'd12; romreg[7]<=4'd14; end else begin for (i=0 ; i<8 ; i=i+1) begin : rom_i romreg[i]<=romreg[i]; //保持不变 end end end assign data = romreg[addr]; //异步输出endmoduleQ5:边沿检测

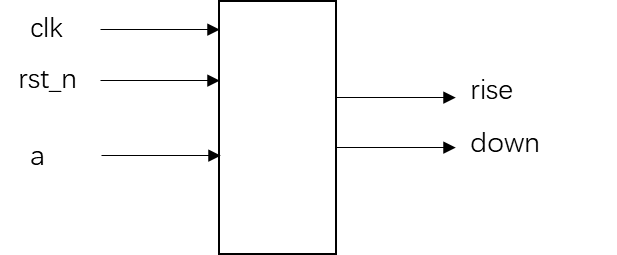

问题描述:有一个缓慢变化的1bit信号a,编写一个程序检测a信号的上升沿给出指示信号rise,当a信号出现下降沿时给出指示信号down。

注:rise,down应为单脉冲信号,在相应边沿出现时的下一个时钟为高,之后恢复到0,一直到再一次出现相应的边沿。

示例输入:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,作为待检测的信号

示例输出:

rise:单比特信号,当输入信号a出现上升沿时为1,其余时刻为0

down:单比特信号,当输入信号a出现下降沿时为1,其余时刻为0

参考代码:

`timescale 1ns/1nsmodule edge_detect( input clk, input rst_n, input a, output wire rise, output wire down); reg a1,a2; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin a1<='b0; a2<='b0; end else begin a1<=a; a2<=a1; end end assign rise = ((a1 & !a2)===1); assign down = ((!a1 & a2)===1);endmodule总结:小白跟大牛都在用的平台

- 硬件工程师近年来也开始慢慢吃香,校招进大厂年薪总包不下30-40w的人数一大把!而且大厂人数并没有饱和!

- 本期是【Verilog刷题篇】硬件工程师从0到入门3|组合逻辑复习+时序逻辑入门,有不懂的地方可以评论进行讨论!

快来点击链接进行跳转注册,开始你的保姆级刷题之路吧!刷题打怪码神之路

另外这里不仅仅可以刷题,你想要的这里都会有,十分适合小白和初学者入门学习~

1、算法篇(398题):面试必刷100题、算法入门、面试高频榜单

2、数据结构篇(300题):都是非常经典的链表、树、堆、栈、队列、动态规划等

3、语言篇(500题):C/C++、java、python入门算法练习

4、SQL篇(82题):快速入门、SQL必知必会、SQL进阶挑战、面试真题

5、大厂笔试真题:字节跳动、美团、百度、腾讯…掌握经验不在惧怕面试!